# Multi-Corner Timing Macro Modeling With Neural **Collaborative Filtering From Recommendation** Systems Perspective

Kevin Kai-Chun Chang, Guan-Ting Liu, Chun-Yao Chiang, Pei-Yu Lee, and Iris Hui-Ru Jiang<sup>10</sup>

Abstract—Timing macro modeling has been widely employed 2 to enhance the efficiency and accuracy of parallel and hierarchi-3 cal timing analysis. However, existing studies primarily focused 4 on generating an accurate and compact timing macro model 5 for single-corner libraries, making it difficult to adapt these 6 approaches to multi-corner situations. This either incurs sub-7 stantial engineering effort or results in significant performance 8 degradation. To tackle this challenge, we offer a fresh per-9 spective on the timing macro modeling problem by drawing 10 inspiration from recommendation systems and formulating it as 11 a matrix completion task. We propose a neural collaborative 12 filtering-based framework capable of capturing the convoluted 13 relationships between circuit pins and timing corners. This frame-14 work enables the precise identification of timing variant regions 15 across different corners. Additionally, we design several training 16 features and implement various training techniques to enhance 17 precision. Experimental results show that our framework reduces 18 model sizes by more than 10% compared to state-of-the-art 19 single-corner approaches, while maintaining competitive tim-20 ing accuracy and exhibiting significant runtime improvements. 21 Furthermore, when applied to unseen corners, our framework 22 consistently delivers superior performance, demonstrating its 23 potential for use in off-corner chiplets in a heterogeneous 24 integration system.

Index Terms-Matrix completion, multiple corners, recommen-25 26 dation systems, timing macro modeling.

#### 27

### I. INTRODUCTION

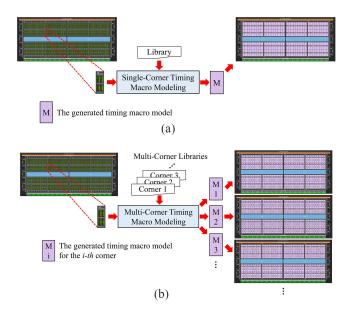

S THE design complexity continues to grow rapidly, 28 timing analysis has become a significant bottleneck of the 29 30 IC design flow. To address this issue, parallel and hierarchical 31 timing analysis is widely adopted, which heavily relies on 32 timing macro modeling. As shown in Fig. 1(a), a large design 33 is first partitioned into several blocks; each block is then 34 analyzed once, and a corresponding timing macro model is

Manuscript received 14 August 2023; revised 7 January 2024; accepted 6 March 2024. This work was supported in part by the National Science and Technology Council, Taiwan. This article was recommended by Associate Editor E. R. Keiter. (Corresponding author: Iris Hui-Ru Jiang.)

Kevin Kai-Chun Chang is with the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720 USA.

Guan-Ting Liu is with NVIDIA Research Taiwan, Taipei 114066, Taiwan. Chun-Yao Chiang is with Synopsys Inc., Taipei 110208, Taiwan.

Pei-Yu Lee is with Synopsys Inc., Hsinchu 300093, Taiwan.

Iris Hui-Ru Jiang is with the Graduate Institute of Electronics Engineering, National Taiwan University, Taipei 106319, Taiwan (e-mail: huirujiang@ ntu.edu.tw)

Digital Object Identifier 10.1109/TCAD.2024.3383350

Fig. 1. Flows of timing macro modeling. (a) Single-corner flow. (b) Multicorner flow. The circuit is the NVIDIA GH100 GPU quoted from [7].

generated to encapsulate the timing properties of the block. 35 Subsequently, the timing macro model can be reused for the 36 same blocks and thus expedites the timing analysis process. In 37 order to generate an accurate and concise timing macro model, 38 timing variant pins (whose timing is affected by primary input 39 (PI) slews or primary output (PO) loading) in a design should 40 be preserved for accuracy, and timing invariant pins can be 41 reduced for compactness. 42

Numerous timing macro modeling approaches have been 43 proposed in the literature. Most of the approaches are algo-44 rithmic, employing a variety of graph-based algorithms during 45 the extraction of timing macro models [1], [2], [3], [4], [5]. 46 In contrast, we present a novel machine learning-based 47 framework in [6]. By incorporating graph neural networks 48 (GNNs), our framework effectively captures timing variant 49 pins, and achieves timing accuracy comparable to state-of-50 the-art algorithmic methods while reducing the model size 51 by 10%. Furthermore, our GNN-based framework can easily 52 be applied to various timing analysis models and modes. 53

With the advancement of semiconductor technology, the 54 timing analysis flow now encompasses the verification of 55 numerous PVT corners (combinations of process, voltage, 56

1

1937-4151 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information.

<sup>57</sup> and temperature parameters) [8]. To ensure that accurate <sup>58</sup> timing analysis can be performed quickly for all the corners, <sup>59</sup> it is crucial to generate a dedicated timing macro model <sup>60</sup> for each corner, as illustrated in Fig. 1(b). However, the <sup>61</sup> aforementioned previous work, including our GNN-based <sup>62</sup> framework, has mainly focused on single-corner timing macro <sup>63</sup> modeling, making it difficult to extend to multi-corner scenar-<sup>64</sup> ios. Accomplishing this either demands substantial engineering <sup>65</sup> efforts or results in timing macro models with diminished <sup>66</sup> accuracy and large sizes. The challenges become even more <sup>67</sup> pronounced when conducting timing analysis on off-corner <sup>68</sup> chiplets, where single-corner approaches are rendered imprac-<sup>69</sup> tical due to the absence of characterized libraries.

The main challenge of multi-corner timing macro modeling 70 71 lies in accurately identifying the difference of timing vari-72 ance on pins for each corner. This is a critical factor in 73 achieving compact model sizes and high-timing accuracy. 74 To tackle this challenge, we formulate the identification 75 problem as a matrix completion task and utilize principles 76 from recommendation systems. We introduce the concept collaborative filtering, which effectively captures simi-77 of 78 larities between pins and utilizes observed data to infer 79 timing variability. Furthermore, we employ neural collab-80 orative filtering (NCF) to model the intricate interactions 81 between pins and corners. Leveraging the neural network <sup>82</sup> layers within the NCF model, we can grasp the complex rela-83 tionships inherent in the multi-corner timing macro modeling problem. 84

The main contributions of this work are summarized as 66 follows.

To the best of our knowledge, our work is the first to

address and formulate the multi-corner timing macro

modeling problem.

We offer a novel recommendation system-based perspective for timing macro modeling and formulate it as a matrix completion problem. This allows us to effectively capture the relationship between pins and corners.

3) We propose a NCF-based framework to learn the intri-94 cate pin-corner interactions. The NCF model not only 95 achieves competitive timing accuracy and reduces macro 96 model sizes by more than 10% compared to the state-97 of-the-art works in million-gate/instance-scale designs, 98 but also demonstrates a 16X faster model training time. 99 Additionally, the NCF model accelerates the training 100 label generation process by 4.4X. 101

4) Our framework consistently preserves exceptional

performance when applied to unseen corners, demon strating its potential for utilization in off-corner chiplets.

The remainder of this article is organized as follows: Section II formulates the single-corner timing macro modeling problem, reviews the previous work on single-corner timmagnetic macro modeling, and details our GNN-based framework proposed in [6]. Section III discusses the challenges and fromulates the multi-corner timing macro modeling problem. Section IV details our multi-corner timing macro modeling framework. Section V shows experimental results. Finally, Section VI concludes this work.

# II. SINGLE-CORNER TIMING MACRO MODELING

114

115

129

### A. Problem Formulation

In this work, we follow the problem formulation from TAU 116 2016 and 2017 contests [9], [10], which is also adopted by 117 most previous work. The *single-corner timing macro modeling* 118 problem can be defined as follows. 119

Given a circuit netlist (\*.v files) along with its parasitics <sup>120</sup> (\*.*spef* files) and the early and late cell libraries (\*.*lib* files), <sup>121</sup> the goal is to generate a timing macro model that encapsulates <sup>122</sup> the timing behaviors of the design. <sup>123</sup>

The generated timing macro model is evaluated based on <sup>124</sup> two primary criteria: 1) timing accuracy (the higher, the better) <sup>125</sup> and 2) the macro model size (the lower, the better). Note that <sup>126</sup> there exists a tradeoff between them. Furthermore, the runtime <sup>127</sup> required to generate the timing macro model is also crucial. <sup>128</sup>

#### B. Previous Work

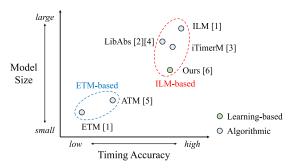

Interface logic models (ILMs) and extracted timing models 130 (ETMs) [1] are two pioneering single-corner timing macro 131 modeling approaches. ILM preserves circuit netlists from PI 132 or PO ports to the first level of registers (i.e., interface 133 logic) while eliminating register-to-register paths. In con- 134 trast, ETM consists solely of context-independent timing 135 arcs between external pins. Subsequent works often build 136 upon either of these two paradigms. Generally, ILM-based 137 approaches [2], [3], [4] achieve exceptionally high-timing 138 accuracy but suffer from larger macro model sizes. Conversely, 139 ETM-based approaches [5] can extract smaller macro models 140 at the expense of timing accuracy. Moreover, ETM-based 141 methods are suitable for IP-reuse scenarios, as they can 142 conceal circuit implementations, while ILM-based methods are 143 more adaptable to advanced timing analysis modes, such as 144 common path pessimism removal (CPPR). 145

For ILM-based approaches, LibAbs [2] and its following <sup>146</sup> work [4] propose several graph reduction techniques that are <sup>147</sup> applied alternately to timing graphs. This iterative process <sup>148</sup> results in a more concise timing macro model. iTimerM [3] <sup>149</sup> divides the circuit netlist into constant and variant timing <sup>150</sup> regions, where the constant timing region is eliminated to <sup>151</sup> achieve compactness. The separation is based on the propagation of minimum/maximum slew values, designating pins <sup>153</sup> with stabilized slew ranges as constant. On the other hand, <sup>154</sup> ATM [5] builds upon the ETM paradigm. It also adopts <sup>155</sup> slew propagation to identify checkpoint pins, which are then <sup>156</sup> inserted into the ETM model to improve timing accuracy. <sup>157</sup> Fig. 2 summarizes the existing single-corner timing macro <sup>158</sup> modeling frameworks.

To facilitate analysis efficiency, the key objective of timing macro modeling is to strike a balance between timing 161 accuracy and the size of the generated timing macro model. 162 Nevertheless, previous work adopts some heuristic techniques 163 during their model extraction, which may cause degradation 164 on the solution quality. For instance, LibAbs [2], [4] applies 165 in-tree and out-tree graph reductions alternatively, based on 166 the observation on the timing arc forms of cells or nets. 167 Besides, some works need to set a threshold for variant pins 168

Fig. 2. Comparison of previous work and our framework.

<sup>169</sup> identification, which requires considerable engineering effort, <sup>170</sup> and the same threshold may not be applicable for various <sup>171</sup> circuit designs. For example, iTimerM [3] uses a threshold <sup>172</sup> to separate the variant regions with the constant region, and <sup>173</sup> ATM [5] uses a threshold to determine which pins are dirty. <sup>174</sup> Therefore, there is still room for improvement.

#### 175 C. Overview of Our GNN-Based Framework

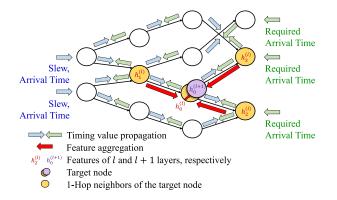

To overcome the deficiencies of prior work, we propose a GNN-based single-corner timing macro modeling frametwork [6]. GNNs have been developed to apply deep learning methods to graph data [11]. In a typical GNN scheme, node information is aggregated and transformed between neighbors recursively. After several neural network layers, a high-level representation of each node is extracted, which encapsulates the features and structures of the node's neighborhood.

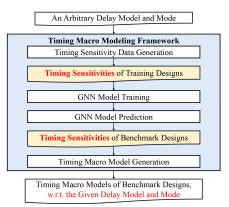

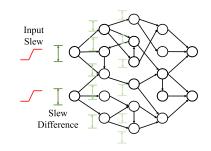

There are several reasons that GNN is suitable for the timing 184 185 macro modeling problem. First, the evaluation of timing criti-186 cality on circuit pins is usually challenging for heuristic-based 187 methods. Nevertheless, graph-learning-based methods could 188 capture implicit properties of circuit pins and thus evaluating 189 timing importance more precisely. Second, the aggregation of <sup>190</sup> node attributes in GNN is similar to the propagation of timing values on timing graphs, as shown in Fig. 3. Consequently, the 191 <sup>192</sup> timing properties of circuit pins could be captured and learned 193 by GNN models smoothly. Third, due to the information 194 exchange mechanism in GNN, the final representations of 195 adjacent nodes tend to become similar. This property is desired <sup>196</sup> in timing macro modeling since neighbor pins are usually of comparable degrees of timing criticality. Lastly, it is natural to 197 198 represent circuit netlists by graphs, and thus GNNs could be <sup>199</sup> easily embedded into the timing macro modeling framework. Fig. 4 illustrates the proposed timing macro modeling 200 <sup>201</sup> framework. In the first stage, the timing sensitivity (TS) of 202 each circuit pin is evaluated to reflect the influence of each <sup>203</sup> pin on the overall timing accuracy. Then, the training data is 204 generated accordingly. In the second stage, we adopt GNN 205 models to learn the properties of circuit designs and predict 206 the timing sensitivities of testing data. Finally, starting from the ILM, timing macro models are generated based on our 207 timing sensitivities prediction. Different from previous work, 208 which mainly focuses on nonlinear delay model (NLDM), 209 210 our framework could also be applied to other advanced node 211 timing analysis models, such as CCS, AOCV, and POCV, 212 or different timing modes like CPPR. The generality of our

Fig. 3. Analogy between GNN aggregation and timing propagation. Timing values, including slew, arrival time, and required arrival time are propagated through edges (blue and green arrows). On the other hand, node features of layer l,  $h_i^{(l)}$ , are aggregated through edges and transformed into node features of layer l + 1,  $h_i^{(l+1)}$  (red arrows).

Fig. 4. Overview of our GNN-based single-corner timing macro modeling framework.

framework comes from the fact that timing sensitivities could <sup>213</sup> be adaptively evaluated depending on the given timing delay <sup>214</sup> model. Moreover, the GNN models could effortlessly capture <sup>215</sup> the corresponding timing properties. <sup>216</sup>

#### D. Timing Sensitivity Data Generation

1) *Timing Sensitivity:* In order to generate a high-quality <sup>218</sup> timing macro model, we need to precisely evaluate the influ-<sup>219</sup> ence of each circuit pin on the timing accuracy of the whole <sup>220</sup> design. Then, pins with subtle influences could be waived to <sup>221</sup> reduce the model size, and meanwhile the timing accuracy will <sup>222</sup> not be degraded. <sup>223</sup>

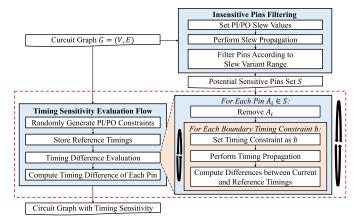

The lower section of Fig. 7 (highlighted by red dashed <sup>224</sup> lines) shows how we evaluate the TS of each pin. Given the <sup>225</sup> input circuit graph, we first randomly generate several sets <sup>226</sup> of boundary timing constraints. For each timing constraint, <sup>227</sup> we store the corresponding timing analysis results of ILM <sup>228</sup> as references. In the TS evaluation stage, we remove a pin <sup>229</sup> from the circuit each time. After the removal, we perform <sup>230</sup> timing propagation based on each set of boundary timing <sup>231</sup> constraints generated and compute the differences between <sup>232</sup> the current and the reference timing values (including slew, <sup>233</sup> arrival time (at), required arrival time (rat), and slack) at the <sup>234</sup> boundary pins. Finally, TS of a pin (for convenience, denoted <sup>235</sup>

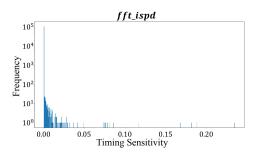

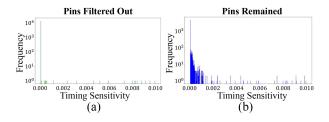

Fig. 5. TS distribution of fft\_ispd.

236 as  $A_i$  in the following discussion) is set as the average of <sup>237</sup> timing value differences under the different timing constraints. <sup>238</sup> Equations (1) and (2) define the TS of pin  $A_i$ , where  $\mathbb{B}$  denotes 239 the collection of generated boundary timing constraints, and <sup>240</sup>  $slew_{P,before}^{b}$  (*resp.*  $slew_{P,after}^{b}$ ) denotes the slew value of a <sup>241</sup> boundary pin *P* under the timing constraint *b* before (*resp.* <sup>242</sup> after) pin  $A_i$ 's removal. The definitions of  $\Delta at_{A_i}^b$ ,  $\Delta rat_{A_i}^b$ , and <sup>243</sup>  $\Delta slack_{A_i}^b$  are similar to that of  $\Delta slew_{A_i}^b$

<sup>244</sup>

$$TS_{A_i} = AVG_{b \in \mathbb{B}} \left( \frac{\Delta slew_{A_i}^b + \Delta at_{A_i}^b + \Delta rat_{A_i}^b + \Delta slack_{A_i}^b}{4} \right)$$

<sup>245</sup> (1)

2

$$_{246} \Delta slew_{A_i}^b = \frac{1}{|PI \cup PO|} \sum_{P \in PI \cup PO} \frac{slew_{P,after}^b - slew_{P,before}^b}{slew_{P,before}^b}.$$

(2)

2) Insensitive Pins Filtering: Although the TS evaluation 247 248 flow could accurately compute the influence of each pin on 249 the overall timing accuracy, running the flow for all the pins time-consuming as we need to perform timing propagation 250 is once in each iteration. To enhance the efficiency, we first 251 observe that the majority of the pins have extremely small 252 even zero TS. It is due to the nature of timing graph that or 253 most of the pins have subtle influences on the overall timing 254 <sup>255</sup> accuracy. For example, the TS distribution of circuit *fft\_ispd* is <sup>256</sup> shown in Fig. 5, where 70% pins have zero TS, while only few pins have large TS. Therefore, if we can find a rapid screening 257 <sup>258</sup> method to filter the insensitive pins first, we could perform TS <sup>259</sup> evaluation flow on the potential critical pins only.

Timing value difference propagation is a suitable method 260 for insensitive pins filtering. At each PI or PO port, two timing 261 values,  $t_{\min}$  and  $t_{\max}$ , are set up. We then propagate the timing 262 values through the design and monitor the difference between 263 <sup>264</sup> the two timing values at each pin. According to the shielding <sup>265</sup> effect, as shown in Fig. 6, the difference decays after several 266 levels, and pins with small difference tend to have subtle <sup>267</sup> influence on the overall timing accuracy. Inspired by previous works [3], [5], we choose slew to propagate from each PI. 268 After the propagation, the slew difference (SD) at each pin is 270 standardized, and pins with SD less than a threshold is filtered <sup>271</sup> out. Fig. 7 illustrates the whole training data generation flow.

# 272 E. GNN-Based Timing Macro Modeling

1) GNN Model Training and Prediction: With the TS 273 274 training data, GNN models could learn and predict accord-275 ingly. In this work, we adopt GraphSAGE [12] as our main 276 GNN engine. For each node v, (3) first aggregates the node

Fig. 6. SD and shielding effect.

Fig. 7. TS training data generation flow.

features from its neighborhood  $\mathcal{N}(v)$ , then (4) concatenates 277 and encodes the representation of node v with the aggregated 278 vector. In the experiments, only four rounds of aggregations 279 and encodings are performed, as the timing property of a node 280 is mostly influenced by its neighborhood. Other existing GNN 281 models, such as GCN [13] or even self-defined GNN models, 282 could also be embedded with our framework 283

$$h_{\mathcal{N}(v)}^{k} \longleftarrow \text{AGGREGATE}_{k}\left(h_{u}^{k-1}, \forall u \in \mathcal{N}(v)\right)$$

(3) 284

$$h_{\nu}^{k} \longleftarrow \sigma \left( W^{k} \cdot \text{CONCAT} \left( h_{\nu}^{k-1}, h_{\mathcal{N}(\nu)}^{k} \right) \right).$$

(4) 285

We treat the GNN prediction as a classification problem and 286 convert the training labels of pins to  $\{0, 1\}$ . A pin's label is set 287 to 1 if its TS is not zero. In addition, for CPPR mode, labels 288 of multiple-fan-out pins of clock networks are also set to 1, as 289 previous work, e.g., [14], suggests their importance for CPPR 290 calculation. 291

The training features are listed in Table I. The features 292 are all basic circuit properties which could be extracted 293 within linear time. Features beginning with "is" are of  $\{0, 1\}$  294 Boolean values. For integer type features like level\_from\_PI, 295 level to PO, and out degree, the values are normalized to 296 [0, 1] so that each feature have the same level of influences. 297

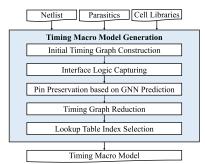

2) Timing Macro Model Generation: Fig. 8 details the 298 timing macro model generation stage. First, we construct the 299 initial timing graph and capture the interface logic netlist 300 to construct ILM. Second, we apply both serial and parallel 301 merging techniques to simplify the timing graph and retain 302 only the timing variant pins identified by the GNN model. For 303 serial merging, the delay of a merged edge is the sum of the 304 original ones, while the slew inherits the last edge. For parallel 305

| Description                                       |

|---------------------------------------------------|

| The minimum level from a PI to the pin            |

| The min. level from the pin to a PO               |

| If the pin is the fanout of a last stage pin      |

| If the pin is the last stage of the timing graph  |

| If the pin is the first stage of the timing graph |

| The number of output edges of the pin             |

| If the pin belongs to clock network               |

| If the pin is the clock pin of a flip-flop        |

| The enumeration number of the cell type           |

| The fan-in size of the rise pin                   |

| The fan-out size of the rise pin                  |

| The fan-in size of the fall pin                   |

| The fan-out size of the fall pin                  |

| If the pin is crucial for CPPR                    |

|                                                   |

TABLE I TRAINING FEATURES

Fig. 8. Timing macro model generation.

<sup>306</sup> merging, delay or slew is the minimum (*resp.* maximum) of the <sup>307</sup> original edge values in the early (*resp.* late) mode. Afterward, <sup>308</sup> we apply the lookup table index selection method proposed <sup>309</sup> in [3], where indices that minimize the interpolation timing <sup>310</sup> error are selected. Lastly, the timing macro model is generated.

#### 311 III. MULTI-CORNER TIMING MACRO MODELING

# 312 A. Corner Explosion and Challenges

With the continuous advances in the semiconductor industry, 313 design verification now involves examinations under numer-314 315 ous PVT corners [8]. This rigorous verification process is 316 essential to ensure the robustness of a design under possible 317 operating conditions. Several approaches have been proposed 318 address the challenges associated with multi-corner timing analysis [15], [16], [17], [18], [19]. Nevertheless, none of 319 320 the previous work has focused on multi-corner timing macro 321 modeling. The groups of timing variant pins may vary a lot 322 across different corners. Consequently, adapting the single-323 corner timing macro modeling frameworks mentioned in 324 Section II to multi-corner settings presents significant engi-325 neering effort or leads to substantial performance degradation. 326 For example, iTimerM [3] and ATM [5] need to fine-tune 327 distinct thresholds for each corner. Similarly, although our <sup>328</sup> single-corner timing macro modeling framework is applicable 329 across different corners, users are still required to extract 330 training data and train an exclusive GNN model for each 331 corner. It becomes even more challenging when dealing with 332 chiplets that deviate from typical corners. To the best of our <sup>333</sup> knowledge, existing approaches lack feasibility in identifying timing variant pins without the presence of a characterized <sup>334</sup> corner library. <sup>335</sup>

### B. Problem Formulation

We extend the problem formulation of single-corner timing <sup>337</sup> macro modeling defined in Section II-A to encompass multicorner settings. The only differences are the input cell libraries <sup>339</sup> are now associated with a set of timing corners, and the <sup>340</sup> framework should generate a dedicated timing macro model <sup>341</sup> for each corner within the corner set or for each unseen corner. <sup>342</sup>

# IV. OUR MULTI-CORNER TIMING MACRO MODELING 343 FRAMEWORK 344

### A. Problem Modeling

The primary challenge of the multi-corner timing macro 346 modeling problem lies in the precise identification of timing 347 variant pins for each corner. This allows us to build a compact 348 timing macro model for each corner while preserving high- 349 timing accuracy. To effectively tackle the issue of identifying 350 timing variant pins, we have discovered that it can be 351 approached from the perspective of recommendation systems 352 because the relationship between pins and corners resembles 353 the user-item relationship in recommendation systems. In the 354 context of recommendation systems, the goal is to capture 355 user-item interactions and provide personalized suggestions. 356 Likewise, in the multi-corner timing macro modeling problem, 357 our objective is to understand the interactions between pin 358 features and corner properties and determine whether a pin 359 is timing variant under a specific corner. By reframing the 360 problem in this manner, we can leverage the well-established 361 techniques from the field of recommendation systems to 362 improve the identification of timing variant pins. 363

A common approach to interpret user-item interactions is to construct a user-item matrix, where each element represents the relationship between the corresponding user and item [20]. Then, it becomes a matrix completion problem that aims to determine the missing entries based on known user-item interactions. Similarly, we can formulate pin-corner relationships as a matrix completion problem. Based on this formulation, our framework has the potential to infer the variability of pins in new designs or assess the degrees of variability under unseen corners.

With this understanding, we can formally define the timing <sup>374</sup> variant pin identification problem in the context of matrix <sup>375</sup> completion, where each circuit pin serves as a user, and each <sup>376</sup> corner is considered an item. The pin-corner matrix  $Y \in \mathbb{R}^{M \times N}$  <sup>377</sup> for *M* pins and *N* corners is defined as <sup>378</sup>

$$y_{A_iC_k} = \begin{cases} 1, & \text{if pin } A_i \text{ is timing variant under corner } C_k \\ 0, & \text{otherwise.} \end{cases}$$

Fig. 9 illustrates the modeling of the pin-corner matrix. The  $_{381}$  goal of the matrix completion process is to determine whether  $_{382}$  each element  $y_{A_iC_k}$  is 0 (pin  $A_i$  is not timing variant under  $_{383}$  corner  $C_k$ ) or 1 ( $A_i$  is timing variant under  $C_k$ ).  $_{384}$

336

|              |   |       |          | Cor      | ner Featu | ires |          |

|--------------|---|-------|----------|----------|-----------|------|----------|

|              |   |       |          |          |           | -    |          |

|              |   |       | Corner 1 | Corner 2 | Corner 3  |      | Corner N |

| s            | ➡ | Pin 1 | 0 / 1    | 0 / 1    | 0 / 1     |      | 0 / 1    |

| Ĩ            | ⇒ | Pin 2 | 0 / 1    | 0 / 1    | 0 / 1     |      | 0 / 1    |

| eat          | ⇒ | Pin 3 | 0 / 1    | 0 / 1    | 0 / 1     |      | 0 / 1    |

| Pin Features | ⇒ | :     | :        | :        | :         | •.   | :        |

| Р            | ⇒ | Pin M | 0 / 1    | 0 / 1    | 0 / 1     |      | 0 / 1    |

Fig. 9. Visualization of a pin-corner matrix.

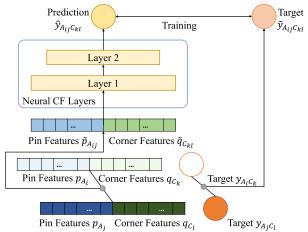

Fig. 10. Structure of the NCF network and data augmentation with mixup.

### 385 B. Collaborative Filtering

398

To address the pin-corner matrix completion problem, we 386 <sup>387</sup> employ the concept of *collaborative filtering*, which identifies shared interests among users, such as the tendency of users, 388 that purchase item A also purchase item B, and leverages this 389 information to provide similar recommendations to users with 390 similar preferences. This attribute is beneficial in the problem 391 of multi-corner timing variant pin identification, as pins with 392 similar properties often exhibit comparable levels of timing 393 variability under the same corner. 394

<sup>395</sup> By employing collaborative filtering, we can express the <sup>396</sup> interaction between the pin  $A_i$  and the corner  $C_k$  as a function <sup>397</sup> of the pin embedding  $p_{A_i}$  and the corner embedding  $q_{C_k}$

$$\hat{y}_{A_iC_k} = f(A_i, C_k | p_{A_i}, q_{C_k}) \tag{6}$$

<sup>399</sup> where *f* can represent any relationship between pin  $A_i$  and cor-<sup>400</sup> ner  $C_k$ . The pin embedding  $p_{A_i}$  and the corner embedding  $q_{C_k}$ <sup>401</sup> can be extracted feature vectors as described in Section IV-C. <sup>402</sup> The interaction function *f* can be optimized by employing <sup>403</sup> target functions that minimize the discrepancy between  $\hat{y}_{A_iC_k}$ <sup>404</sup> and  $y_{A_iC_k}$ , where  $y_{A_iC_k}$  refers to the corresponding element in <sup>405</sup> the pin-corner matrix as described in (5).

# 406 C. Neural Collaborative Filtering (NCF) and Training 407 Features

Since the identification of timing variant pins involves many factors (e.g., topological complexity, operating condition), it is crucial to find an interaction function f that can capture nonlinear relationships between pin features and their timing variability under different corners. Thus, we employ the NCF model [20], which consists of fully connected neural

TABLE II Corner Features for Training

| Feature             | Description                                                    |

|---------------------|----------------------------------------------------------------|

| process             | The process of the corner (fast: 0.9, typical: 0.6, slow: 0.3) |

| voltage             | The operating voltage of the corner                            |

| temperature         | The operating temperature of the corner                        |

| inv_cell_rise       | The flattened cell-rise lookup table of the inverter           |

| inv_rise_transition | The flattened rise-transition lookup table of the inverter     |

| inv_cell_fall       | The flattened cell-fall lookup table of the inverter           |

| inv_fall_transition | The flattened fall-transition lookup table of the inverter     |

network layers, as shown in Fig. 10. In contrast to simple 414 interaction functions, such as the inner product, the NCF 415 model demonstrates the potential to capture complex and 416 nonlinear relationships between pins and corners. 417

In our NCF model, each input vector consists of the pin <sup>418</sup> feature vector  $p_{A_i}$  and the corner feature vector  $q_{C_k}$ . For <sup>419</sup> pin features, we adopt the same circuit topology features <sup>420</sup> as our single-corner timing macro modeling framework, as <sup>421</sup> described in Table I and Section II-E1. On the other hand, <sup>422</sup> as shown in Table II, corner features include the temperature, <sup>423</sup> voltage, and process of the corner. Furthermore, given that an <sup>424</sup> inverter consists of a pMOS and an nMOS, it can effectively <sup>425</sup> represent the switching characteristics of the corresponding <sup>426</sup> corner library. Thus, we also incorporate the elements in the <sup>427</sup> timing lookup tables of the inverter cell as our corner features. <sup>428</sup> Lookup tables of other primitive cells (e.g., NAND, AND, <sup>429</sup> etc.) might also be included to further enhance the model's <sup>430</sup> learning quality. <sup>431</sup>

After the extraction and concatenation of pin features  $p_{A_i}$  <sup>432</sup> and corner features  $q_{C_k}$ , the corresponding timing variability <sup>433</sup>  $\hat{y}_{A_iC_k}$  can be inferred as follows: <sup>434</sup>

$$\hat{y}_{A_iC_k} = f_{\Phi}\left(\left[p_{A_i}, q_{C_k}\right]\right) \tag{7} \quad 435$$

where  $[\cdot, \cdot]$  is the concatenation operator, and  $f_{\Phi}$  is the 436 interaction function with a set of parameters  $\Phi$ .

In our NCF model, we use two layers of fully connected  $_{438}$  neural network. Thus, the interaction function  $f_{\Phi}$  can be further  $_{439}$  expressed as  $_{440}$

$$f_{\Phi}\left(\left[p_{A_{i}}, q_{C_{k}}\right]\right) = \sigma\left(f_{\Phi_{2}}\left(\tanh\left(f_{\Phi_{1}}\left(\left[p_{A_{i}}, q_{C_{k}}\right]\right)\right)\right)\right)$$

(8) 441

where  $\Phi = {\Phi_1, \Phi_2}, \Phi_1$ , and  $\Phi_2$  correspond to the parameters of the first and the second NCF layer, respectively, tanh(·) 443 denotes the hyperbolic tangent function which serves as the 444 activation function, and  $\sigma(\cdot)$  is the sigmoid function which 445 maps the predicted values to the range of [0, 1]. 446

Since the target  $y_{A_iC_k}$  of each training data  $[p_{A_i}, q_{C_k}]$  is of a <sup>447</sup> binary value, we adopt the binary classification loss function <sup>448</sup> to optimize the model <sup>449</sup>

$$\mathcal{L} = -\sum_{(A_i, C_k) \in \mathbb{X}} y_{A_i C_k} \log \hat{y}_{A_i C_k} + (1 - y_{A_i C_k}) \log(1 - \hat{y}_{A_i C_k})$$

<sup>450</sup>

(9) 451

where X denotes the training label set which will be discussed 452 in Section IV-D. We use the Adam optimizer [21] to minimize 453 the loss defined by (9). Other design choices (e.g., increasing 454 the number of neural network layers, using different activation 455 functions, etc.) might be adopted to further improve the 456 performance. 457

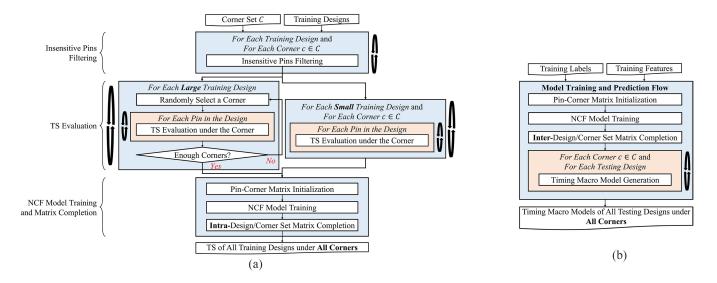

Fig. 11. (a) Training label generation flow. (b) Flow of NCF model training, prediction, and timing macro model generation on testing data.

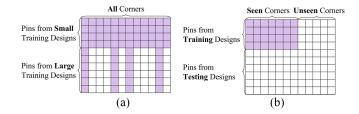

Fig. 12. (a) Intra-design/corner set matrix completion. (b) Inter-design/corner set matrix completion. Initially, timing variability in the purple region is known, while the goal is to infer the timing variability of the white region.

#### 458 D. Training Label Generation

To enhance the capability of timing variant pin identification 459 of our NCF model, high-quality training labels are essential. 460 Drawing from the achievements of our single-corner timing 461 macro modeling framework, we leverage two key processes, 462 463 insensitive pins filtering and TS evaluation, to generate our 464 training labels. The details of these processes are presented <sup>465</sup> in Fig. 7 and Section II-D. By extending the concepts of (1) 466 and (2), we can define the TS in the context of multi-corner 467 timing macro modeling

$$\operatorname{TS}_{A_{i}C_{k}} = \operatorname{AVG}_{b \in \mathbb{B}} \left( \frac{\Delta slew_{A_{i}C_{k}}^{b} + \Delta at_{A_{i}C_{k}}^{b} + \Delta rat_{A_{i}C_{k}}^{b} + \Delta slack_{A_{i}C_{k}}^{b}}{4} \right)$$

$$(10)$$

470

$$\Delta slew_{A_iC_k}^b = \frac{1}{|PI \cup PO|} \sum_{P \in PI \cup PO} \frac{slew_{PC_k, \text{after}}^b - slew_{PC_k, \text{before}}^b}{slew_{PC_k, \text{before}}^b}$$

(11)

<sup>471</sup> where  $TS_{A_iC_k}$  denotes the TS of pin  $A_i$  under timing corner  $C_k$ , <sup>472</sup>  $\mathbb{B}$  denotes the set of boundary timing constraints,  $slew_{PC_k, before}^{b}$ <sup>473</sup> and  $slew^b_{PC_k, after}$  denote the slew value at boundary pin *P* under <sup>474</sup> corner  $C_k$  before and after the removal of  $A_i$ , respectively, <sup>475</sup> and  $\Delta at_{A_iC_k}^{b}$ ,  $\Delta rat_{A_iC_k}^{b}$ , and  $\Delta slack_{A_iC_k}^{b}$  can be obtained similar <sup>476</sup> to (11). After the TS evaluation, we have to convert the TS 477 values into binary to fill in the pin-corner matrix. In our work, <sup>478</sup> a pin  $A_i$  is deemed timing variant under a corner  $C_k$  if and only

if the corresponding TS is larger than a threshold  $t_{\nu}$ . That is 479

$$y_{A_iC_k} = \begin{cases} 1, & \text{if } \operatorname{TS}_{A_iC_k} > t_v \\ 0, & \text{otherwise} \end{cases}$$

(12) 480

where  $t_v$  is set as 0.0001 in our experiments.

However, the computational cost of the TS evaluation flow 482 increases linearly with the number of corners, making it 483 excessively time-consuming to evaluate TS for all pins across 484 all corners, particularly in large-scale training designs. To 485 expedite the generation of training labels, we also incorporate 486 NCF model and matrix completion into our training label 487 generation flow, as depicted in Fig. 11(a). Our approach begins 488 by performing insensitive pins filtering on each corner and 489 design, which involves a one-time timing propagation and 490 therefore does not consume significant time. Subsequently, 491 only the pins that have not been filtered out in at least one of 492 the corners are considered for the TS evaluation step. For each 493 large training design, we randomly select a subset of corners 494 and generate TS values for the remaining pins under those 495 corners, while TS values of small training design are generated 496 across all corners. Then, we convert TS values to timing 497 variability and build the pin-corner matrix. By employing 498 NCF model training and prediction, we can infer the timing 499 variability for the unselected corners. Fig. 12(a) visualizes the 500 matrix completion process. Timing variability for all pins from 501 small training designs is already known, whereas for pins in 502 large training designs, timing variability is only evaluated for 503 a subset of corners. The goal is to infer the timing variability 504 within the white part. Given that the known timing variability 505 spans across all designs and corners, we refer to this approach 506 as intra-design/corner set matrix completion. 507

#### E. Training Techniques—Data Augmentation With mixup 508

Now, intuitively, we can utilize the training features from 509 Tables I and II and the training labels generated from 510 Section IV-D to start the training of our NCF model. However, 511 due to the nature of timing graphs, few pins are actually 512

<sup>513</sup> influential in the overall timing accuracy. Consequently, there <sup>514</sup> exists a scarcity of positive elements (i.e.,  $y_{A_iC_k} = 1$ ) in <sup>515</sup> the pin-corner matrix (less than 10% in most designs). The <sup>516</sup> overwhelmingly large portion of timing invariant data makes <sup>517</sup> it hard for the model to distinguish critical but rare timing <sup>518</sup> variant pins from hundreds of thousands of pins in a large <sup>519</sup> circuit design. To mitigate the label imbalance issue, we utilize <sup>520</sup> *mixup* [22], a simple yet effective data-augmentation approach <sup>521</sup> that generates pseudo-training data by interpolation.

We first group all pin-corner pairs with training label 1 as the positive set  $\mathbb{X}^+$  :  $\{(A_i, C_k) | (A_i, C_k) \in \mathbb{X} \text{ and} \}$ 224  $y_{A_iC_k} = 1\}$  and those with training label 0 as the negative set 225  $\mathbb{X}^-$  :  $\{(A_j, C_l) | (A_j, C_l) \in \mathbb{X} \text{ and } y_{A_jC_l} = 0\}$ . In each training 226 iteration, for each pin-corner pair  $(A_i, C_k)$  in  $\mathbb{X}^+$ , we sample 227 one pin-corner pair  $(A_j, C_l)$  from the negative set  $\mathbb{X}^-$ . Then, 228 the corresponding pin and corner features form a feature tuple 229  $(p_{A_i}, q_{C_k}, p_{A_j}, q_{C_l})$ . After that, we interpolate each data pair 230 with a coefficient  $\lambda$  sampled from the Beta distribution to 231 generate the augmented data

532

$$\tilde{p}_{A_{ij}} = \lambda p_{A_i} + (1 - \lambda) p_{A_j}$$

$$\tilde{q}_{C_{kl}} = \lambda q_{C_k} + (1 - \lambda) q_{C_l}$$

534

$$\tilde{\mathcal{Y}}A_{ij}C_{j}$$

533

$$\tilde{y}_{A_{ij}C_{kl}} = \begin{cases} 1, & \text{if } \lambda y_{A_iC_k} + (1-\lambda)y_{A_jC_l} > 0.5 \\ 0, & \text{otherwise.} \end{cases}$$

<sup>535</sup> After generating the augmented data  $(\tilde{p}_{A_{ij}}, \tilde{q}_{C_{kl}}, \tilde{y}_{A_{ij}C_{kl}})$ , we can <sup>536</sup> optimize the NCF model by rewriting the loss function (9) as <sup>537</sup> follows:

538

$$\mathcal{L} = -\sum_{(A_i, C_k) \in \mathbb{X}^+} [\tilde{y}_{A_{ij}C_{kl}} \log \hat{y}_{A_{ij}C_{kl}} + (1 - \tilde{y}_{A_{ij}C_{kl}}) \log(1 - \hat{y}_{A_{ij}C_{kl}})]$$

540 where

541  $\hat{y}_{A_{ii}C_{kl}} = f_{\Phi}([\tilde{p}_{A_{ii}}, \tilde{q}_{C_{kl}}]).$

As shown in Fig. 10, by interpolating the pin and corner fat features with opposite timing variability, the model is forced to learn more comprehensive and distinguishable features for timing variant pins and thus make more precise inferences on fate new layouts or unseen corners.

# 547 F. Testing Data Prediction

After completing the training label generation and data augmentation, we perform NCF model training and prediction to identify timing variant pins in the testing designs, as shown in Fig. 11(b). Unlike the intra-design/corner set matrix completion discussed in Section IV-D, where the timing variability of pins from all designs is known, in this case, the matrix completely unseen testing designs. Furthermore, we assume that there may exist unseen corners in the testing data. Therefore, we refer to this approach as *inter-design/corner set matrix completion*. Fig. 12(b) visualizes this matrix completion process.

Once we have identified the timing variant pins, we proceed to generate timing macro models for each testing design under each corner, employing a process similar to single-corner

TABLE III

TRAINING DESIGN STATISTICS. IN EXPERIMENTS REGARDING THE Acceleration of Training Label Generation in Section V-C4, the Left 13 Designs Serve as "Small" Training Designs While the Right Six Designs Are "Large" Training Designs

| Design       | #Pins | #Cells | #Nets | Design       | #Pins | #Cells | #Nets |

|--------------|-------|--------|-------|--------------|-------|--------|-------|

| s1196_eval   | 2181  | 823    | 791   | usb_funct    | 48243 | 15992  | 15911 |

| s1494_eval   | 2584  | 976    | 951   | systemcaes   | 21971 | 6873   | 6790  |

| s27_eval     | 94    | 40     | 36    | wb_dma       | 13125 | 4627   | 4419  |

| s344_eval    | 638   | 251    | 225   | tv80         | 17038 | 5331   | 5317  |

| s349_eval    | 651   | 261    | 235   | ac97_ctrl    | 42438 | 14473  | 14435 |

| s386_eval    | 641   | 245    | 232   | pci_bridge32 | 59879 | 19426  | 19274 |

| s400_eval    | 760   | 287    | 260   |              |       |        |       |

| s510_eval    | 980   | 382    | 369   |              |       |        |       |

| s526_eval    | 1002  | 381    | 354   |              |       |        |       |

| crc32d16N    | 1283  | 527    | 495   |              |       |        |       |

| usb_phy_ispd | 2545  | 957    | 938   |              |       |        |       |

| systemcdes   | 10282 | 3638   | 3596  |              |       |        |       |

| aes_core     | 66751 | 23327  | 23199 |              |       |        |       |

TABLE IV Testing Designs Statistics

| Design                   | #Pins   | #Cells  | #Nets   |

|--------------------------|---------|---------|---------|

| mgc_edit_dist_iccad_eval | 581319  | 224113  | 224101  |

| vga_lcd_iccad_eval       | 768050  | 286597  | 286498  |

| leon3mp_iccad_eval       | 4167632 | 1534489 | 1534410 |

| netcard_iccad_eval       | 4458141 | 1630171 | 1630161 |

| leon2_iccad_eval         | 5179094 | 1892757 | 1892672 |

| mgc_edit_dist_iccad      | 450354  | 164266  | 164254  |

| vga_lcd_iccad            | 679258  | 259251  | 259152  |

| leon3mp_iccad            | 3376832 | 1248058 | 1247979 |

| netcard_iccad            | 3999174 | 1498565 | 1498555 |

| leon2_iccad              | 4328255 | 1617069 | 1616984 |

| mgc_matrix_mult_iccad    | 492568  | 176084  | 174484  |

timing macro modeling, as depicted in Fig. 8. The distinction 563 lies in the pin preservation step, which is now determined 564 based on the pin-corner matrix. 565

#### V. EXPERIMENTAL RESULTS

566

567

#### A. Experimental Settings

In our framework, the training and prediction of both NCF 568 models and GNN models are implemented in the Python3 569 programming language, while the insensitive pins filtering, 570 TS evaluation, and timing macro model generation are implemented in the C++ programming language. The experiments 572 are conducted on a Linux workstation with a 3.7-GHz CPU, 573 192 GB RAM, and an NVIDIA RTX 3090 GPU. 574

For the experiments regarding single-corner timing macro 575 modeling, we adopt the benchmark suite provided by the 576 TAU 2016 [9] and TAU 2017 [10] contests as listed in 577 Tables III and IV. For the experiments regarding multi-corner 578 timing macro modeling, we also adopt the circuit designs 579 from these two contests. As for the multi-corner library, we 580 adopt the Synopsys SAED 32/28nm Digital Standard Cell 581 Library [23], as the TAU libraries do not support multi- 582 corner functionality. We use 27 base characterization corners 583 in our experiments, as listed in Table V. The first and second 584 characters in a corner's name denote its nMOS and pMOS 585 processes, respectively, (f, t, and s represent fast, typical, 586 and slow, respectively). The central segment of a corner's 587 name signifies the voltage, while the final segment denotes 588 the temperature. For instance, "tt1p05vn40c" corresponds to 589 typical nMOS and pMOS processes, 1.05 V, and -40°C. In 590 each corner library, a total of 314 cells are characterized. We 591

TABLE V Corner List

| ff0p85v125c | ff0p85v25c  | ff0p85vn40c | ff0p95v125c | ff0p95v25c  |

|-------------|-------------|-------------|-------------|-------------|

| ff0p95vn40c | ff1p16v125c | ff1p16v25c  | ff1p16vn40c | ss0p7v125c  |

| ss0p7v25c   | ss0p7vn40c  | ss0p75v125c | ss0p75v25c  | ss0p75vn40c |

| ss0p95v125c | ss0p95v25c  | ss0p95vn40c | tt0p78v125c | tt0p78v25c  |

| tt0p78vn40c | tt0p85v125c | tt0p85v25c  | tt0p85vn40c | tt1p05v125c |

| tt1p05v25c  | tt1p05vn40c |             |             |             |

have aligned the cell names in TAU 2016 and TAU 2017 circuit

netlists with those in the SAED libraries.

In our experiments, we assess timing accuracy by comparing the timing analysis results of the timing macro model with the flat circuit design. We adopt iTimerC 2.0 [14] as the reference timer. On the other hand, the evaluation of macro model size is based on the size of the early library associated with the timing macro model.

# 600 B. Results on Single-Corner Timing Macro Modeling

First, we evaluate our single-corner timing macro modeling framework and compare the results with state-of-the-art works. Note that in our experiments, we utilize only the first eight basic features in Table I, along with the *is\_CPPR* feature. This selection is made to enhance the overall performance.

Table VI shows the results on TAU 2016 [9] and TAU 606 607 2017 [10] benchmarks considering CPPR and the compar-<sup>608</sup> isons with two state-of-the-art ILM-based works iTimerM [3] and [4]. Among all the criteria, max error and model file size 609 610 are viewed as the most crucial ones. Our framework achieves 611 extremely high-timing accuracy as all the max errors are less 612 than 0.1 ps, which is same as iTimerM [3] and 9 times better 613 than [4]. As for model file size, our result is about 10% smaller 614 than iTimerM [3] and 45% smaller than [4]. To summarize, 615 our framework preserves the highest-timing accuracy in terms 616 of max errors among the state-of-the-art works, while further 617 improving the model size by 10% than the same-accuracy-618 level work. Our framework also achieves similar or even better 619 results in terms of model generation performance and model usage performance. The average errors of our framework 620 are slightly higher than those of iTimerM [3]; however, 621 622 the difference is only a few femtoseconds and thus can be 623 neglected.

In Table VII, we demonstrate how domain knowledge can 624 625 enhance GNN model training across various timing models 626 or modes, using CPPR as a case study. As mentioned in 627 Section II-E, multiple-fan-out pins of clock networks are 628 crucial for CPPR calculation. Thus, we could add a dedicated 629 training feature for CPPR to indicate this kind of pins, 630 called *is CPPR*. We adopt the results of iTimerM [3] as the 631 baseline and calculate the differences and ratios as described 632 in Table VI. Before adding is CPPR, our framework could 633 already achieve the same timing accuracy as iTimerM [3] while reducing the model size by 6%. After the is CPPR 634 635 feature is included, our framework still preserves the same 636 timing accuracy while improving the model size by 10%. The 637 result tells that our framework could achieve superior quality 638 with only the basic features, while the dedicated features could 639 capture the timing properties of designs more precisely.

Fig. 13. Separated TS distribution of *systemcaes* based on the insensitive pins filtering.

Table VIII displays the results on the TAU 2017 [10] <sup>640</sup> benchmark without CPPR. Our results are compared with <sup>641</sup> the ILM-based work iTimerM [3] and the ETM-based work <sup>642</sup> ATM [5]. In comparison with ATM [5], our framework <sup>643</sup> achieves 9 times better-max error and 25 times better-average <sup>644</sup> error, but it suffers from a larger model size. It is as our <sup>645</sup> expectation since our framework is ILM-based while ATM [5] <sup>646</sup> is ETM-based. Besides, we also achieve 17 times faster model <sup>647</sup> generation runtime than ATM [5]. As for the ILM-based work <sup>648</sup> iTimerM [3], we preserve the same timing accuracy while <sup>649</sup> improving the model size by 9%. The result demonstrates <sup>650</sup> the applicability and generality of our framework on different <sup>651</sup> timing modes (CPPR on and CPPR off), and it may be further <sup>652</sup> inferred to various timing delay models and modes.

As mentioned in Section II-D, the goal of the insensitive 654 pins filtering is to exclude noncritical pins rapidly, under the 655 premise that the timing accuracy is not degraded. Fig. 13 656 shows the timing sensitivities of pins in the training design 657 systemcaes. TS of pins that are filtered out are shown in the 658 left histogram, and those of the potential sensitive pins are 659 shown in the right histogram. It can be seen that a majority 660 of filtered pins indeed have zero TS, while many remained 661 pins have nonzero TS. It confirms the consistency between the 662 insensitive pins filtering and the TS evaluation, which implies 663 the insensitive pins filtering is suitable for accelerating the 664 training data generation flow. To further ensure the timing 665 accuracy is not degraded by the insensitive pins filtering, we 666 conduct an experiment in which the training labels of all the 667 remained pins after the insensitive pins filtering are set to 1. 668 The result is shown in Table IX. The results of iTimerM [3] 669 are adopted as the baseline, and the differences and ratios are 670 calculated as described in Table VI. The results achieve the 671 same timing accuracy as iTimerM [3] which is of the best 672 accuracy among the previous works. Therefore, it is supported 673 that the insensitive pins filtering does not degrade the resulting 674 timing accuracy. 675

Finally, when we encounter new benchmarks under the same <sup>676</sup> NLDM libraries, we only need to consider the GNN model <sup>677</sup> inference runtime and the model generation runtime since our <sup>678</sup> framework is available on general designs under the NLDM. <sup>679</sup> The GNN model inference time is usually much less than <sup>680</sup> the model generation time listed in the above tables. Thus, <sup>681</sup> our framework spends comparable or even shorter runtime <sup>682</sup> than previous work for unseen test data under the NLDM. As <sup>683</sup> for other timing delay models, such as AOCV, POCV, and <sup>684</sup> CCS, we need to further consider the training data generation <sup>685</sup> time and the GNN model training time. However, since our <sup>686</sup>

#### TABLE VI

SINGLE-CORNER TIMING MACRO MODELING EXPERIMENTAL RESULTS ON TAU 2016 [9] AND TAU 2017 [10] BENCHMARKS WITH CPPR. FOR THE MODEL FILE SIZE, WE ADOPT THE SIZE OF THE LIBRARY FOR LATE TIMING. DIFFERENCE 1 AND RATIO 1 ARE COMPARED WITH ITIMERM [3]. DIFFERENCE 2 AND RATIO 2 ARE COMPARED WITH [4]. DIFFERENCE = COMPARED RESULT – OUR RESULT. RATIO = COMPARED RESULT/OUR RESULT. NOTE THAT [4] IS ONLY EVALUATED ON TAU 2016 BENCHMARK IN THEIR WORK

| Design                   |              | Avg.<br>Error | Max<br>Error |         | Model<br>File Size | Generation<br>Runtime | Generation<br>Memory | Usage<br>Runtime | Usage<br>Memory |

|--------------------------|--------------|---------------|--------------|---------|--------------------|-----------------------|----------------------|------------------|-----------------|

|                          |              | (ps)          | (ps)         |         | (MB)               | (s)                   | (MB)                 | (s)              | (MB)            |

|                          | Ours         | 0.0000        | 0.007        | Ours    | 56                 | 11                    | 1087                 | 8                | 475             |

| mgc_edit_dist_iccad_eval | iTimerM      | 0.0000        | 0.007        | iTimerM | 64                 | 10                    | 1043                 | 8                | 550             |

|                          | [4]          | N.A.          | 0.158        | [4]     | 79                 | 15                    | 5                    | 4                | 5               |

|                          | Ours         | 0.0006        | 0.040        | Ours    | 45                 | 12                    | 1204                 | 6                | 383             |

| vga_lcd_iccad_eval       | iTimerM      | 0.0006        | 0.040        | iTimerM | 50                 | 13                    | 1208                 | 7                | 402             |

|                          | [4]          | N.A.          | 0.255        | [4]     | 72                 | 24                    | 399                  | 4                | 5               |

|                          | Ours         | 0.0004        | 0.052        | Ours    | 35                 | 50                    | 4908                 | 5                | 324             |

| leon3mp_iccad_eval       | iTimerM      | 0.0004        | 0.052        | iTimerM | 45                 | 58                    | 4807                 | 6                | 395             |

|                          | [4]          | N.A.          | 0.220        | [4]     | 86                 | 78                    | 5                    | 5                | 5               |

|                          | Ours         | 0.0000        | 0.004        | Ours    | 213                | 89                    | 6609                 | 29               | 1757            |

| netcard_iccad_eval       | iTimerM      | 0.0000        | 0.004        | iTimerM | 220                | 65                    | 6513                 | 29               | 1822            |

|                          | [4]          | N.A.          | 0.203        | [4]     | 372                | 101                   | 12616                | 23               | 4332            |

|                          | Ours         | 0.0002        | 0.016        | Ours    | 369                | 89                    | 8298                 | 64               | 3034            |

| leon2_iccad_eval         | iTimerM      | 0.0002        | 0.016        | iTimerM | 372                | 82                    | 7865                 | 61               | 3056            |

|                          | [4]          | N.A.          | 0.241        | [4]     | 676                | 105                   | 15299                | 38               | 5315            |

| TALL 2016 American       | Difference 1 | 0.0000        | 0.000        | Ratio 1 | 1.116              | 0.961                 | 0.975                | 1.099            | 1.094           |

| TAU 2016 Average         | Difference 2 | N.A.          | 0.192        | Ratio 2 | 1.809              | 1.448                 | 0.818                | 0.738            | 0.851           |

| man adit diat issaid     | Ours         | 0.0029        | 0.052        | Ours    | 60                 | 16                    | 1054                 | 8                | 514             |

| mgc_edit_dist_iccad      | iTimerM      | 0.0003        | 0.052        | iTimerM | 66                 | 12                    | 1063                 | 9                | 537             |

| was lad issued           | Ours         | 0.0024        | 0.080        | Ours    | 56                 | 16                    | 1455                 | 7                | 474             |

| vga_lcd_iccad            | iTimerM      | 0.0023        | 0.080        | iTimerM | 58                 | 15                    | 1429                 | 8                | 487             |

| 1                        | Ours         | 0.0031        | 0.046        | Ours    | 37                 | 68                    | 5407                 | 5                | 332             |

| leon3mp_iccad            | iTimerM      | 0.0016        | 0.046        | iTimerM | 46                 | 67                    | 5281                 | 6                | 406             |

|                          | Ours         | 0.0013        | 0.029        | Ours    | 239                | 101                   | 7814                 | 35               | 1938            |

| netcard_iccad            | iTimerM      | 0.0003        | 0.029        | iTimerM | 248                | 98                    | 7545                 | 33               | 1993            |

| 1                        | Ours         | 0.0027        | 0.095        | Ours    | 438                | 125                   | 8171                 | 62               | 3613            |

| leon2_iccad              | iTimerM      | 0.0013        | 0.095        | iTimerM | 440                | 109                   | 8049                 | 64               | 3625            |

| TAU 2017 Average         | Difference   | -0.0013       | 0.000        | Ratio   | 1.084              | 0.903                 | 0.984                | 1.070            | 1.065           |

TABLE VII SINGLE-CORNER TIMING MACRO MODELING EXPERIMENTAL RESULTS WITH AND WITHOUT CPPR-DEDICATED FEATURES

| Benchmark      |                   | Avg.<br>Error | Max<br>Error |              | Model<br>File Size | Generation<br>Runtime | Generation<br>Memory | Usage<br>Runtime | Usage<br>Memory |

|----------------|-------------------|---------------|--------------|--------------|--------------------|-----------------------|----------------------|------------------|-----------------|

| TAU2016 (avg.) | Difference Before | 0.0000        | 0.000        | Ratio Before | 1.064              | 1.055                 | 0.959                | 1.133            | 1.048           |

| IA02010 (avg.) | Difference After  | 0.0000        | 0.000        | Ratio After  | 1.116              | 0.961                 | 0.975                | 1.099            | 1.094           |

| TAU2017 (avg.) | Difference Before | -0.0001       | 0.000        | Ratio Before | 1.060              | 0.828                 | 0.994                | 1.115            | 1.037           |

| TAU2017 (avg.) | Difference After  | -0.0013       | 0.000        | Ratio After  | 1.084              | 0.903                 | 0.984                | 1.070            | 1.065           |

<sup>687</sup> framework could be directly applied to perform timing macro <sup>688</sup> modeling no matter which timing model is chosen, users do <sup>689</sup> not need to spend a great deal of time designing specific <sup>690</sup> algorithms for different timing delay models and tuning a <sup>691</sup> bunch of parameters. As a consequence, our framework still <sup>692</sup> shows high applicability and efficiency on the timing macro <sup>693</sup> modeling problem.

# 694 C. Results on Multi-Corner Timing Macro Modeling

*1) Effectiveness of Our Multi-Corner Framework:* In this section, we compare our multi-corner timing macro modeling framework with the multi-corner extensions of state-of-theart single-corner timing macro modeling frameworks. The results of iTimerM [3] are obtained by directly conducting the iTimerM algorithm flow on each specific corner. For the experiments of our single-corner timing macro modeling framework (hereafter referred to as "[6]" to avoid ambiguity rog in this section), training data for each corner is generated first, and subsequently distinct GNN models are trained for each rof individual corner.

<sup>706</sup> To ensure fair comparisons, for experiments in <sup>707</sup> Sections V-C1 and V-C2, all the training designs from Table III are categorized as "small" during the training label 708 generation process (as shown in Fig. 11); that is, the timing 709 variability of all the pins is evaluated under all the corners. 710 Note that LibAbs [2], [4] and ATM [5] do not support the 711 multi-corner SAED library, and thus they are not included in 712 the comparison in this section. 713

Table X presents the experimental results on TAU 2016 and 714 TAU 2017 benchmarks listed in Table IV over the 27 corners. 715 Here, the "average" max error (*resp.* model size) represents 716 the mean values of the maximum timing errors (*resp.* timing 717 macro model size) across the 27 corners, while the "max" 718 max error (*resp.* model size) indicates the highest values of the 719 maximum timing errors (*resp.* timing macro model size) across 720 the 27 corners. Note that the results in Table X are without 721 CPPR because the SAED library does not provide separate 722 early and late cell libraries. Nevertheless, incorporating CPPR 723 into our framework would pose no significant challenge, as 724 we can easily integrate the *is\_CPPR* feature in our pin feature 725 vector. 726

Compared to the state-of-the-art algorithmic work 727 iTimerM [3], our framework demonstrates a 16% improvement 728 in model size while maintaining the same level of timing 729 accuracy, with an average max error difference of less than 730

SINGLE-CORNER TIMING MACRO MODELING EXPERIMENTAL RESULTS ON TAU 2017 BENCHMARK WITHOUT CPPR. DIFFERENCE 1 AND RATIO 1 ARE COMPARED WITH ITIMERM [3]. DIFFERENCE 2 AND RATIO 2 ARE COMPARED WITH ATM [5]. DIFFERENCE = COMPARED RESULT – OUR RESULT. RATIO = COMPARED RESULT/OUR RESULT. WE ADDITIONALLY INCLUDE THE CIRCUIT mgc\_matrix\_mult\_iccad TO EVALUATE SINCE ATM [5] ALSO ADOPTS IT AS ONE TEST CASE

| Design                |              | Avg.<br>Error<br>(ps) | Max<br>Error<br>(ps) |         | Model<br>File Size<br>(MB) | Generation<br>Runtime<br>(s) | Generation<br>Memory<br>(MB) | Usage<br>Runtime<br>(s) | Usage<br>Memory<br>(MB) |

|-----------------------|--------------|-----------------------|----------------------|---------|----------------------------|------------------------------|------------------------------|-------------------------|-------------------------|

|                       | Ours         | 0.0033                | 0.052                | Ours    | 59                         | 14                           | 1069                         | 9                       | 563                     |

| mgc_edit_dist_iccad   | iTimerM      | 0.0007                | 0.052                | iTimerM | 65                         | 13                           | 1062                         | 9                       | 523                     |

|                       | ATM          | 0.0960                | 0.402                | ATM     | 2                          | 833                          | N.A.                         | 0.36                    | N.A.                    |

|                       | Ours         | 0.0026                | 0.080                | Ours    | 52                         | 18                           | 1457                         | 7                       | 442                     |

| vga_lcd_iccad         | iTimerM      | 0.0023                | 0.080                | iTimerM | 55                         | 17                           | 1420                         | 9                       | 450                     |

|                       | ATM          | 0.0400                | 0.160                | ATM     | 0.3                        | 85                           | N.A.                         | 0.06                    | N.A.                    |

|                       | Ours         | 0.0033                | 0.046                | Ours    | 31                         | 78                           | 5392                         | 5                       | 275                     |

| leon3mp_iccad         | iTimerM      | 0.0018                | 0.046                | iTimerM | 31                         | 102                          | 5257                         | 4                       | 286                     |

|                       | ATM          | 0.1070                | 0.460                | ATM     | 0.6                        | 740                          | N.A.                         | 0.09                    | N.A.                    |

|                       | Ours         | 0.0033                | 0.029                | Ours    | 226                        | 124                          | 7804                         | 32                      | 1795                    |

| netcard_iccad         | iTimerM      | 0.0005                | 0.029                | iTimerM | 229                        | 104                          | 7539                         | 33                      | 1838                    |

|                       | ATM          | 0.0540                | 0.246                | ATM     | 1.6                        | 618                          | N.A.                         | 0.27                    | N.A.                    |

|                       | Ours         | 0.0027                | 0.095                | Ours    | 408                        | 193                          | 8156                         | 60                      | 3378                    |

| leon2_iccad           | iTimerM      | 0.0013                | 0.095                | iTimerM | 410                        | 152                          | 7782                         | 59                      | 3390                    |

|                       | ATM          | 0.0400                | 0.240                | ATM     | 2.4                        | 1055                         | N.A.                         | 0.34                    | N.A.                    |

|                       | Ours         | 0.0032                | 0.054                | Ours    | 124                        | 27                           | 1106                         | 18                      | 924                     |

| mgc_matrix_mult_iccad | iTimerM      | 0.0020                | 0.054                | iTimerM | 171                        | 29                           | 1114                         | 24                      | 1098                    |

|                       | ATM          | 0.1300                | 0.450                | ATM     | 12                         | 629                          | N.A.                         | 1.63                    | N.A.                    |

| Average               | Difference 1 | -0.0016               | 0.000                | Ratio 1 | 1.093                      | 0.980                        | 0.978                        | 1.085                   | 1.033                   |

| Average               | Difference 2 | 0.0748                | 0.267                | Ratio 2 | 0.028                      | 17.910                       | N.A.                         | 0.029                   | N.A.                    |

TABLE IX VALIDATION ON INSENSITIVE PINS FILTERING

| Benchmark | Avg. Error | Max Error | Model File Size |

|-----------|------------|-----------|-----------------|

| TAU2016   | 0.0000     | 0.000     | 1.040           |

| TAU2017   | 0.0000     | 0.000     | 1.009           |

731 0.2 ps. Moreover, considering the maximum of max error 732 and model size, our framework reduces the timing macro 733 model size by over 20% while maintaining a timing error difference of less than 0.1 ps. Compared to the learning-734 735 based approach [6], our framework exhibits a similar trend, showcasing a 10% improvement in average model size while 736 737 keeping the timing error difference below 0.2 ps. Similarly, 738 the results are even better when considering the maximum of 739 max error and model size. The experimental results validate 740 the precise identification of timing variant pins in each corner 741 by our framework, leading to highly compact timing macro 742 models. Furthermore, the superior performance observed in 743 terms of the maximum of max error and model size suggests 744 that our framework effectively captures the relationship 745 between each pin and each specific corner, ensuring stable 746 performance across all corners.

In addition to timing accuracy and timing macro model 747 748 size, our framework also exhibits outstanding performance 749 in terms of runtime. As shown in Table XI(a), our framework achieves approximately a 16X faster model training 750 time compared to [6]. The main reason is that the GNN 751 752 models used in our single-corner framework [6] are specific each corner. Consequently, experiments of [6] necessitated 753 to 754 training 27 separate GNN models. In contrast, our NCF 755 model in our multi-corner framework accounts for all the 756 designs and corners involved and thus requires only one <sup>757</sup> model that merely takes 4.12 s per training epoch. It is 758 important to note that the time spent on model tuning has not been considered here, and it is obvious that fine-tuning 759 the parameters for 27 models is much more time-consuming 760 than for a single model. The speedups will be even more 761 significant for advanced technology nodes with hundreds or 762 even thousands of corners. Furthermore, Table XI(b) compares 763 the time required to identify and generate a file containing the 764 timing variant pins for the 11 designs listed in Table IV for 765 one corner. All three frameworks exhibit similar performance 766 in this aspect. Additionally, it is worth noting that our 767 framework is able to identify timing variant pins for unseen 768 designs. Therefore, it is reasonable to compare the model 769 inference time of our framework with the overall runtime of 770 iTimerM [3].

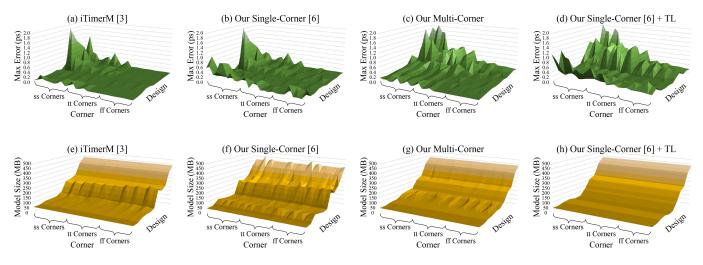

To further analyze the results of multi-corner timing 772 macro modeling, we present 3-D surface plots that illustrate 773 variations in maximum errors and model sizes for various 774 corners and designs, as depicted in Fig. 14. These visual- 775 izations are based on the experimental results presented in 776 Tables X and XII. Each of the surface plots contains 297 777 data points (27 corners  $\times$  11 designs). In comparison with 778 model sizes, the max errors show more drastic changes across 779 various corners. This phenomenon aligns with the inherent 780 characteristics of timing macro models, wherein the mere 781 addition or removal of a small number of timing-critical 782 pins can induce significant alterations in timing behavior. 783 Nevertheless, our multi-corner framework maintains a max 784 error of less than 2.0 ps for all the corners and designs, 785 which is comparable to the existing works. Additionally, we 786 can observe from Fig. 14(f) that the model sizes of our 787 single-corner framework [6] fluctuate wildly across different 788 corners. It is as expected given that this approach necessitates 789 a unique GNN model for each corner. Consequently, this 790 model-by-model strategy may result in unstable performance 791 due to the uncertainties inherent in the training processes 792 for each GNN instance. In contrast, as shown in Fig. 14(g), 793

#### TABLE X

Multi-corner Timing Macro Modeling Experimental Results on TAU 2016 and TAU 2017 Benchmarks Over 27 Corners. Average Error and Max Error Are Compared by Difference, Where Difference = Compared Result – Our Result. Macro Model Size Is Compared Based on Ratio, Where Ratio = Compared Result/Our Result

|                          | iTimerM [3] |         |         |          |         | Our Single-Corner [6] |         |         |           |         |            | Our N   | /ulti-Cori |          |         |

|--------------------------|-------------|---------|---------|----------|---------|-----------------------|---------|---------|-----------|---------|------------|---------|------------|----------|---------|

| Design                   | Average     | Max Err | or (ps) | Model Si | ze (MB) | Average               | Max En  | or (ps) | Model Siz | ze (MB) | Average    | Max Err | or (ps)    | Model Si | ze (MB) |

|                          | Error (ps)  | average | max     | average  | max     | Error (ps)            | average | max     | average   | max     | Error (ps) | average | max        | average  | max     |

| mgc_edit_dist_iccad_eval | 0.0005      | 0.217   | 1.293   | 66.7     | 69.0    | 0.0008                | 0.183   | 0.613   | 87.4      | 101.0   | 0.0188     | 0.702   | 1.855      | 54.1     | 55.0    |

| vga_lcd_iccad_eval       | 0.0005      | 0.064   | 0.309   | 65.4     | 78.0    | 0.0017                | 0.284   | 0.878   | 65.2      | 68.0    | 0.0005     | 0.067   | 0.309      | 80.2     | 96.0    |

| leon3mp_iccad_eval       | 0.0004      | 0.118   | 1.031   | 47.0     | 47.0    | 0.0004                | 0.133   | 1.031   | 31.8      | 33.0    | 0.0058     | 0.491   | 1.031      | 36.0     | 36.0    |

| netcard_iccad_eval       | 0.0005      | 0.188   | 1.838   | 219.7    | 220.0   | 0.0008                | 0.219   | 1.838   | 198.3     | 225.0   | 0.0021     | 0.352   | 1.838      | 203.9    | 205.0   |

| leon2_iccad_eval         | 0.0004      | 0.146   | 1.771   | 375.0    | 376.0   | 0.0008                | 0.183   | 1.771   | 345.5     | 360.0   | 0.0046     | 0.309   | 0.599      | 371.6    | 373.0   |

| mgc_edit_dist_iccad      | 0.0002      | 0.006   | 0.008   | 68.0     | 73.0    | 0.0003                | 0.017   | 0.072   | 74.9      | 86.0    | 0.0096     | 0.185   | 0.343      | 60.0     | 60.0    |

| vga_lcd_iccad            | 0.0004      | 0.042   | 0.225   | 88.9     | 101.0   | 0.0016                | 0.232   | 0.969   | 71.9      | 77.0    | 0.0006     | 0.096   | 0.225      | 90.3     | 112.0   |

| leon3mp_iccad            | 0.0003      | 0.078   | 0.132   | 46.0     | 47.0    | 0.0003                | 0.078   | 0.132   | 33.5      | 36.0    | 0.0013     | 0.132   | 0.249      | 36.3     | 37.0    |

| netcard_iccad            | 0.0002      | 0.028   | 0.044   | 247.2    | 248.0   | 0.0003                | 0.031   | 0.062   | 246.8     | 258.0   | 0.0014     | 0.124   | 0.226      | 232.3    | 237.0   |

| leon2_iccad              | 0.0003      | 0.085   | 0.112   | 435.5    | 436.0   | 0.0003                | 0.102   | 0.146   | 412.7     | 462.0   | 0.0010     | 0.141   | 0.240      | 432.9    | 433.0   |

| mgc_matrix_mult_iccad    | 0.0003      | 0.034   | 0.132   | 231.4    | 278.0   | 0.0005                | 0.127   | 0.264   | 229.7     | 259.0   | 0.0074     | 0.516   | 0.871      | 118.4    | 119.0   |

| Diffrence / Ratio        | -0.0045     | -0.192  | -0.081  | 1.168    | 1.203   | -0.0041               | -0.139  | -0.001  | 1.103     | 1.177   | 0.0000     | 0.000   | 0.000      | 1.000    | 1.000   |

Fig. 14. 3-D surface plots of max errors and model sizes across corners and designs.

<sup>794</sup> our multi-corner framework consistently demonstrates similar

<sup>795</sup> model sizes across diverse corners, indicating its adaptability

<sup>796</sup> to various, and potentially unseen, timing corners.